# Cost effectiveness filter design for low-latency audio analogue to digital converter (Σ-ΔADC)

Xiangyu Zhu

A thesis submitted in partial fulfilment of the requirements of

Birmingham City University for the degree of Doctor of Philosophy

June 2021

Digital Media Technology Lab,

The Faculty of Computing, Engineering and the Built Environment,

**Birmingham City University**

#### Abstract

The current technical challenge posed in professional audio industry is to have a small size portable device, which can support real-time interactive applications.  $\Sigma$ - $\Delta$  Modulation based audio system becomes the mainstream due to the higher resolution and fewer auxiliary circuits. However, extremely high sampling frequency brings severe challenges to its decimation or interpolation filter design and performance. The current optimal filter design parameter calculation methods have room for improvement, such as complex calculations and results need further rounding. Therefore, Author proposed a new optimal decimation or interpolation rate selection approach converts the optimization problem to factorization and permutation problem which improves the efficiency significantly and provides directly usable integer solutions. Furthermore, due to the lack of theoretical relationship between latency of filter and multi-stage design parameters a latency estimation equation is derived by author. The analysis of this equation shows that optimal computational cost design and optimal latency design have contradictory requirements. Hence, the optimization of filter design parameter is added to optimize the other costs as much as possible. Thus, author proposed a new numeric optimization based method to design the cost efficient low-latency multi-stage multi-rate filter. This approach further reduces the costs of the filter on the basis of the previous optimal design. At last, a MATLAB GUI based filter design and evaluation framework has been established which can help user to search the optimal design parameters and design optimal filters with different filter types.

#### Acknowledgements

I'd like to thank everyone in the Digital Media Technology (DMT) Lab at Birmingham City University and Prof. We Hu's team in Wuhan University of Science and Technology. In particular my supervisor Prof. Cham, Dr. Yonghao Wang and Prof. We Hu who supported and encouraged me alot during my PhD research. Also, a big thank you to all my dear friends for their help and support not only in research but also mentally and daily life. Finally, to my family, thank you. None of these would have happened without you.

## Acronyms

| PDE  | Partial Differential Equations        |

|------|---------------------------------------|

| IC   | Integrated Circuit                    |

| VLSI | Very Large Scale Integration          |

| DSP  | Digital Signal Processing (Processor) |

| LTI  | Linear Time-Invariant                 |

| ADC  | Analogue to Digital Converter         |

| DAC  | Digital to Analogue Converter         |

| FIR  | Finite Impulse Response               |

| IIR  | Infinite Impulse Response             |

| CIC  | Cascaded Integrator-Comb              |

| PCM  | Pulse-code Modulation                 |

| SDM  | Sigma-Delta Modulation                |

| FFT  | Fast Fourier Transform                |

| DTFT | Discrete-time Fourier Transform       |

| DFT  | Discrete Fourier Transform            |

| SRC  | Sampling Rate Conversion (Changing)   |

| SNR  | Signal-Noise Ratio                    |

| SA   | Simulated Annealing                   |

| GUI  | Graphic User Interface                |

|      |                                       |

## Mathematical Notation

| $\mathbb{N}_1$            | Set of Natural Numbers                   |  |

|---------------------------|------------------------------------------|--|

| $\sum_{i=1}^{K} D_i$      | Accumulation from $D_1$ to $D_K$         |  |

| $\prod_{i=1}^{K} D_i$     | Multiplication from $D_1$ to $D_K$       |  |

| $\binom{n}{k}$ or $C_k^n$ | Binomial coefficient or all combinations |  |

| $\Delta f$                | Transition bandwidth                     |  |

| $\delta_1$                | Passband ripple                          |  |

| $\delta_2$                | Stopband attenuation                     |  |

| $f_p$                     | Passband edge                            |  |

| $f_s$                     | Stopband edge                            |  |

| $F_s$                     | Sampling frequency                       |  |

| D                         | Oversampling rate                        |  |

| K                         | Number of stage                          |  |

| $\nabla$                  | Partial derivative of vector             |  |

## Contents

| 1        | Intr | oduction                                                          | 1  |

|----------|------|-------------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                        | 1  |

|          | 1.2  | Aim and Objectives                                                | 2  |

|          | 1.3  | Thesis Structure                                                  | 3  |

|          | 1.4  |                                                                   | 5  |

|          | 1.5  |                                                                   | 7  |

| <b>2</b> | Lite | erature Review                                                    | 8  |

|          | 2.1  | Digital Audio System                                              | 8  |

|          |      | - ·                                                               | 9  |

|          |      | 2.1.2 $\Sigma$ - $\Delta$ Modulation Based Digital Audio System 1 | 1  |

|          | 2.2  |                                                                   | 3  |

|          |      | 2.2.1 LTI Discrete-Time System                                    | 3  |

|          |      | 2.2.2 Infinite Impulse Response (IIR) Filter                      | 6  |

|          |      | , ,                                                               | 7  |

|          |      | 2.2.4 Discussion                                                  | 9  |

|          | 2.3  | Filter Cost                                                       | 9  |

|          |      | 2.3.1 Different Filter Cost                                       | 9  |

|          |      | 2.3.2 Latency                                                     |    |

|          |      |                                                                   | 23 |

|          |      |                                                                   | 24 |

|          | 2.4  | Optimal Decimation/Interpolation Rate Calculation Methods 2       |    |

|          |      | 2.4.1 Optimal Computational Cost(Crochiere and Rabiner            |    |

|          |      |                                                                   | 8  |

|          |      | 2.4.2 Optimal Memory Usage(Crochiere and Rabiner 1976) . 2        |    |

|          |      | 1 0 0 0                                                           | 0  |

|          |      | 2.4.4 Improved Optimal Memory Usage(Coffey 2007) 3                |    |

|          | 2.5  | • • • • /                                                         | 34 |

| 3        | Met  | thodology 30                                                      | 6  |

| 4        | $\cos$ | t Efficient Decimation Rate Selection and Filter Design                                           | 40        |

|----------|--------|---------------------------------------------------------------------------------------------------|-----------|

|          | 4.1    | Limitations of Existing Approaches                                                                | 40        |

|          | 4.2    | Description of the Background                                                                     | 41        |

|          |        | 4.2.1 Computational Cost                                                                          | 42        |

|          |        | 4.2.2 Area Cost                                                                                   | 44        |

|          | 4.3    | Optimal Decimation/Interpolation Rate Selection Approach .                                        | 46        |

|          | 4.4    | Knowledge Based Search and 3D Database                                                            | 54        |

|          | 4.5    | Summary                                                                                           | 56        |

| <b>5</b> | Res    | earch and Derivation for Theoretical Latency of Multi-                                            |           |

|          | stag   | ge Multi-rate Filter                                                                              | <b>58</b> |

|          | 5.1    | Background                                                                                        | 58        |

|          | 5.2    | Decimation Rate Distribution for Low Latency Filter Design .                                      | 59        |

|          |        | 5.2.1 Equation Derivation                                                                         | 59        |

|          |        | 5.2.2 Analysis the Properties of Equation                                                         | 62        |

|          | 5.3    | Discussion of Low Latency Filter Design                                                           | 64        |

|          |        | 5.3.1 Verification Test $\ldots$                                                                  | 65        |

|          |        | 5.3.2 Other Considerations for Groupdelay Optimization                                            | 68        |

|          | 5.4    | Summary                                                                                           | 72        |

| 6        |        | V Latency Cost Efficient Filter Design Using Optimization                                         |           |

|          |        | thod                                                                                              | <b>74</b> |

|          | 6.1    | Limitation of Current Filter Design Method                                                        | 74        |

|          | 6.2    | Cost Efficient Filter Design Using Halfband Filter                                                | 76        |

|          | 6.3    | Search the Optimal Solution Using Simulated Annealing Al-                                         |           |

|          |        | gorithm                                                                                           | 81        |

|          | 6.4    | Results and Analysis                                                                              | 86        |

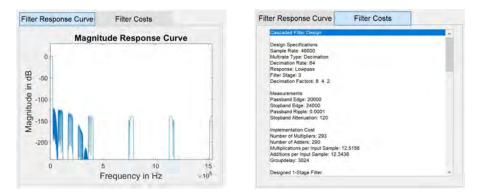

|          | 6.5    | MATLAB GUI Based Filter Design and Evaluation Framework                                           | 90        |

|          |        | 6.5.1 Brief Introduction                                                                          | 90        |

|          |        | 6.5.2 GUI Working Principle                                                                       | 91        |

|          |        | 6.5.3 Conclusion $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 94        |

| <b>7</b> | Cor    | clusion and Future Work                                                                           | 95        |

|          | 7.1    | Conclusion                                                                                        | 95        |

|          | 7.2    | Critique and Future Work                                                                          | 97        |

| Re       | efere  | nce                                                                                               | 99        |

## List of Figures

| 1.1  | Structure of Research                                                    | 3  |

|------|--------------------------------------------------------------------------|----|

| 2.1  | Audio Processing Chain                                                   | 8  |

| 2.2  | Pulse-code Modulation                                                    | 9  |

| 2.3  | Input Signal and Harmonic Signal                                         | 10 |

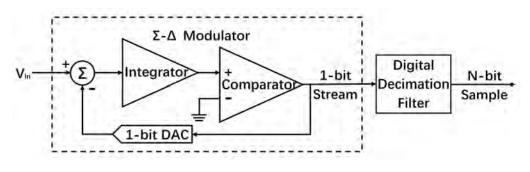

| 2.4  | Block Diagram for $\Sigma$ - $\Delta$ ADC                                | 11 |

| 2.5  | First-Order $\Sigma$ - $\Delta$ ADC                                      | 12 |

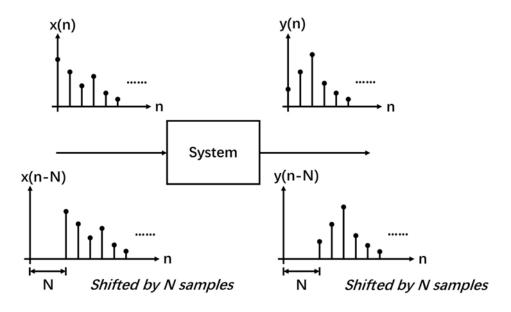

| 2.6  | Sketched Diagram of Time Invariance                                      | 14 |

| 2.7  | Sketched Diagram of Linear System                                        | 15 |

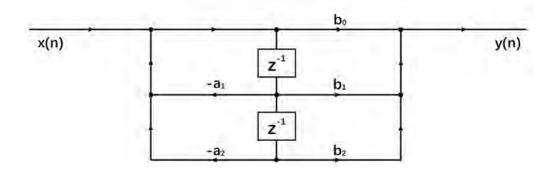

| 2.8  | Second-Order IIR Filter Simplified Notation                              | 16 |

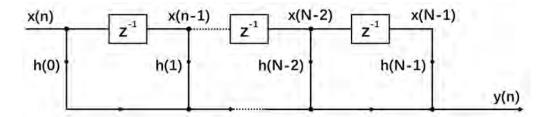

| 2.9  | $N_{th}$ Order FIR Filter Simplified Notation                            | 18 |

| 2.10 | $3_{rd}$ Order FIR Filter Simplified Notation                            | 20 |

| 2.11 | Relationship Between Different Filter Design Aspects                     | 23 |

| 2.12 | Sketched Block Diagram of Crochiere and Rabiner (1975)                   | 27 |

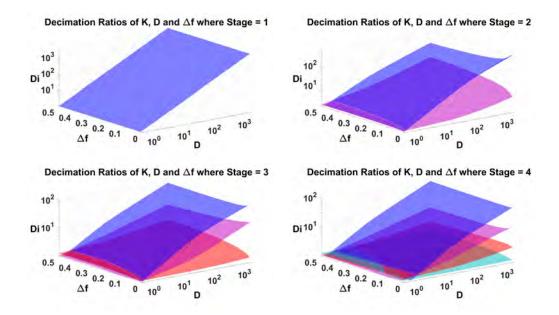

| 4.1  | Distribution of Minimized 'S' (Crochiere and Rabiner, 1975) $\therefore$ | 42 |

| 4.2  | Decimation Rate Distribution of Optimal Computational Cost               |    |

|      | Filter Design                                                            | 43 |

| 4.3  | Distribution of Minimized 'T' (Crochiere and Rabiner, 1976) $\therefore$ | 45 |

| 4.4  | Decimation Rate Distribution of Optimal Area Cost Filter De-             |    |

|      | sign                                                                     | 45 |

| 4.5  | Flow Chart of Finding the Optimal Solution for N-Stage Filter            |    |

|      | Design                                                                   | 48 |

| 4.6  | Flow Chart of Factor Reduction for N-Stage Filter Design                 | 50 |

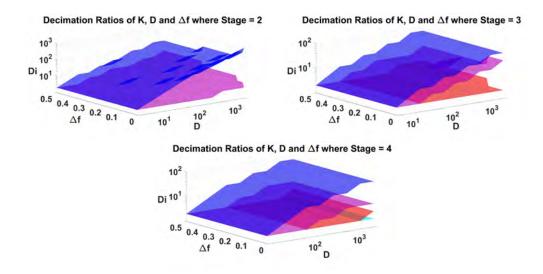

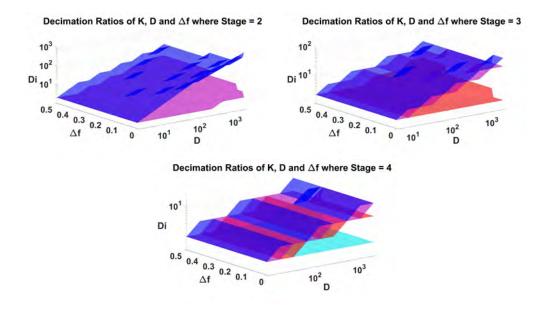

| 4.7  | Integer Solution Sets Distribution for $D = 2^n$ (Computational)         | 53 |

| 4.8  | Integer Solution Sets Distribution for $D = 2^n$ (Area)                  | 54 |

| 4.9  | Changing of Optimal Value against $\Delta f$ for Composite Number        |    |

|      | D                                                                        | 55 |

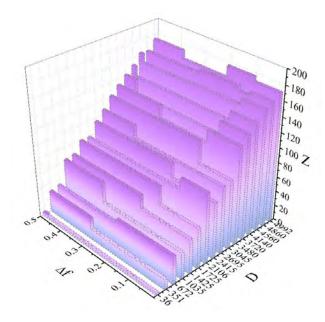

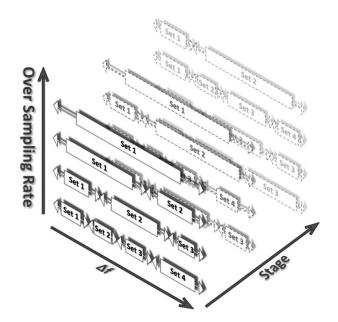

| 4.10 | Sketched 3-dimensional storage matrix for Database                       | 56 |

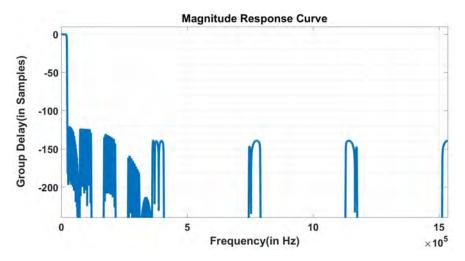

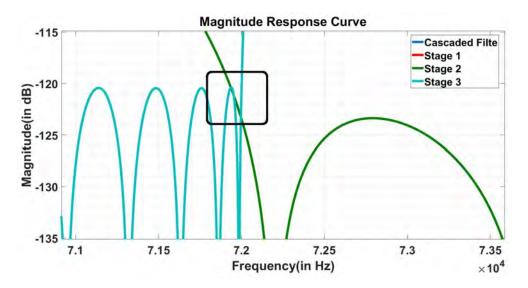

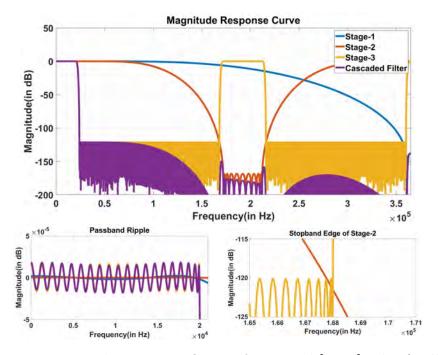

| 5.1  | Magnitude Response Curve of Designed Filter                              | 69 |

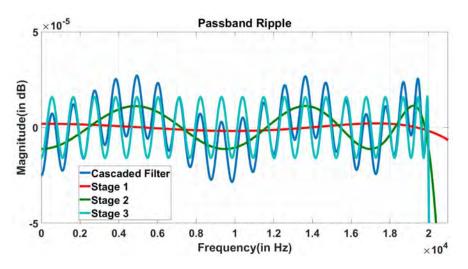

| 5.2  | Passband Ripple of Designed Filter and Each Stage                        | 70 |

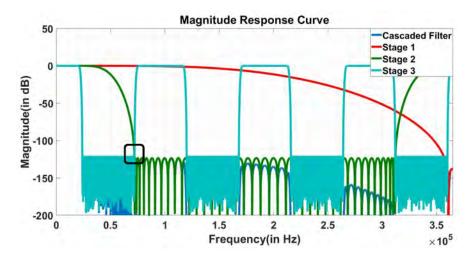

| 5.3  | Stopband Edge and Attenuation of Designed Filters             | 71  |

|------|---------------------------------------------------------------|-----|

| 5.4  | Details of Filter's Stopband Edge and Attenuation             | 71  |

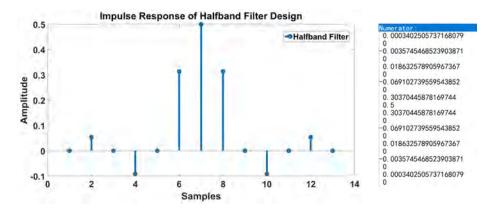

| 6.1  | Impulse Response and Coefficients of Halfband Filter Design . | 77  |

|      | 1 I                                                           | • • |

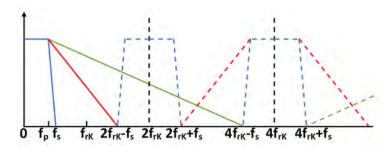

| 6.2  | Schematic Diagram of Multi-stage Multi-rate Filter Design     | 77  |

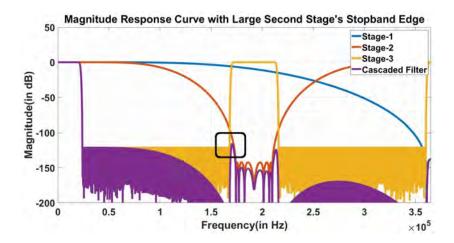

| 6.3  | Diagram of Overshoot Problem in Multi-stage Filter Design .   | 78  |

| 6.4  | Magnitude Response Curve of Designed [8 2 4] Filter(Halfband) | 79  |

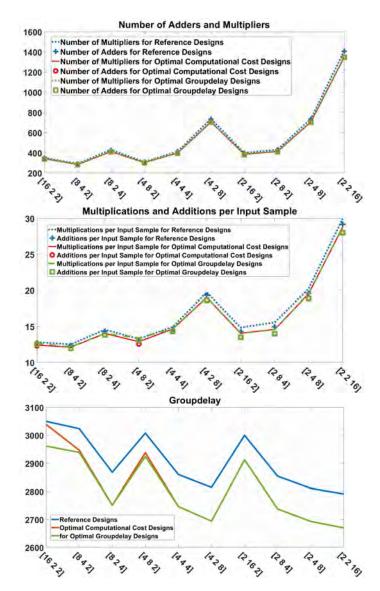

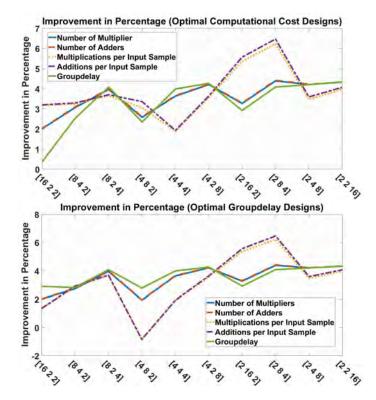

| 6.5  | Improvement of Low Latency Cost Efficient Designs             | 88  |

| 6.6  | Improvement of Low Latency Cost Efficient Designs(Percentage) | 89  |

| 6.7  | Interface of Filter Design and Evaluation Framework           | 90  |

| 6.8  | Interface of Output Magnitude Response Curve and Filter Costs | 91  |

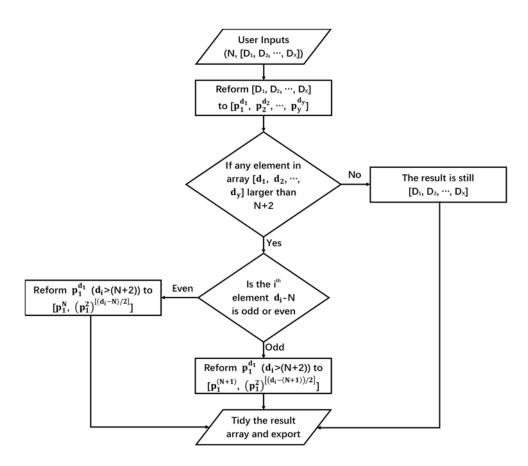

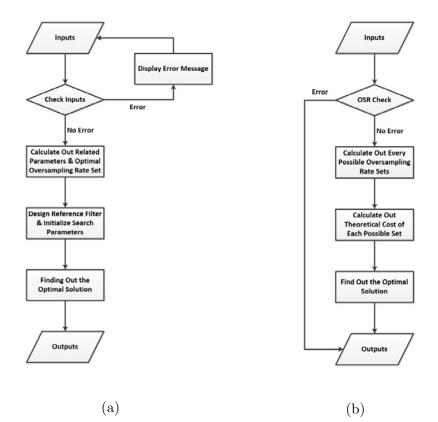

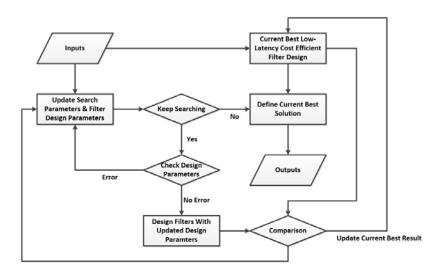

| 6.9  | Flow Chart of Filter Design and Evaluation Framework 1        | 92  |

| 6.10 | Flow Chart of Filter Design and Evaluation Framework 2        | 93  |

## List of Tables

| 2.1 | Comparison Between FIR and IIR Filters                        | 19 |

|-----|---------------------------------------------------------------|----|

| 4.1 | Test Conditions                                               | 43 |

| 4.2 | Characteristic for 1-5000 non-prime numbers                   | 50 |

| 4.3 | Search the Optimal Distribution Solution                      | 52 |

| 5.1 | Test Conditions                                               | 65 |

| 5.2 | Costs for Single Stage Filter Design                          | 65 |

| 5.3 | Decimation Rate Distribution and Costs for 2-Stage Filter     | 66 |

| 5.4 | Decimation Rate Distribution and Costs for 3-Stage Filter     | 66 |

| 5.5 | Filter Design Specifications of Example                       | 68 |

| 5.6 | Related Parameters of Designed Filter                         | 69 |

| 6.1 | Filter Design Requirements                                    | 75 |

| 6.2 | Filter Design Requirements for each stage                     | 76 |

| 6.3 | Designed [8 2 4] Filter's Costs and Groupdelay                | 79 |

| 6.4 | Matrix of Search Direction                                    | 82 |

| 6.5 | MATLAB Code for Search Direction Matrix Calculation           | 83 |

| 6.6 | Control Group for Low Latency Cost Efficient Filter Design .  | 86 |

| 6.7 | Best Results for Low Latency Cost Efficient Filter Design(CC) | 87 |

| 6.8 | Best Results for Low Latency Cost Efficient Filter Design(GD) | 87 |

## Chapter 1

## Introduction

## 1.1 Motivation

At present, the development of science and technology has a great impact on human entertainment activities. The digital technology especially has a great influence on the professional audio industry. The interesting technical challenge posed in professional audio industry is to have a small size portable device, which can support real-time interactive (with low latency) applications.

Nowadays, more and more entertainment functions are embedded in the portable devices, such as using smartphones and tablet devices to play, control and interact with audio data. Due to the limitation of the physical size and power supply, the hardware efficiency has become more and more important to the system design, in other words, the design needs to achieve the maximum effect with minimum resources. This puts a challenge on both analogue and digital design parts of the audio system. For the digital part, the hardware efficiency normally means the architecture with fewer digital logical gates to perform arithmetic operations.

For larger audio performance shows in live, the professional audio processing system chain is used in real-time for live mixing and monitoring, audio processing, live broadcasting, and live recording. It is well known that the distinguishable latency for human ear is about 30ms (Haas 1972). According to Lester and Boley (2007), the audio latency in the scale of a few milliseconds can be perceived by human ear, especially in the professional studio or live concert. In the article Lester and Boley (2007), the perceptions of musicians who play different musical instruments are tested by using different latencies for live sound monitoring devices. For some musicians, the very low latency in-ear monitoring system is preferred in which the latency is less than 2ms, for example: singers and saxophonists.

The current professional audio processing systems can be separated into analog based system and digital based system. The analogue based system has a strong ability of audio signal restoration and an extremely low group delay. However, the analog based system normally has a large volume and power cost due to the application of a large number of analog components. Kester (2015) stated that with the development of technology, the  $\Sigma$ - $\Delta$  Modulation, which uses high sampling frequency to trade for high sample resolution is developed and the capabilities of hardware are improved. This means the digital system could have enough resolution to achieve high level audio processing. At the same time, the digital system has the advantages of low power cost and portability over to analogue system. Therefore, the current trend is to use digital system to process high resolution audio signal.

Although the volume and power cost of digital system has been greatly improved compared to analog system, it still cannot fully meet the increasing stringent requirements for portability. Also, the current digital devices are battery powered. Therefore, efficient digital systems have become the trend of design. Hence, the computational cost which cause the most power cost become an important indicator to measure a digital system design.

According to Wang, Stables, and Reiss (2010), Reiss (2008) and above introduction presented, it can be known that the challenge basically raises two technical aspects in terms of digital domain:

- 1. Hardware efficient digital filter design for audio signal processing.

- 2. Real-time DSP algorithm and architecture with low latency.

Therefore, it is interesting to concentrate on the technical challenges of design hardware efficient low latency  $\Sigma$ - $\Delta$  based ADC.

## 1.2 Aim and Objectives

The aim of this research is to carry out a comprehensive evaluation as well as propose a framework for the digital filter design with both low latency and low cost for  $\Sigma$ - $\Delta$  modulation based ADC/DAC.

In order to achieve this goal, several objectives are set up.

- 1 Investigate into the optimal decimation or interpolation rate calculation methods and improve the current approach.

- 2 Explore the relationship between latency and filter design parameters; and derive the latency estimation equation.

- 3 Explore the optimal filter design parameters finding method, and propose the optimal filter design approach based on optimal design parameters.

- 4 Develop cost efficient low-latency filter design optimization method and evaluation framework using numeric optimization algorithm.

## **1.3** Thesis Structure

Based on the aim and objectives, the sketched research structure can be constructed as:

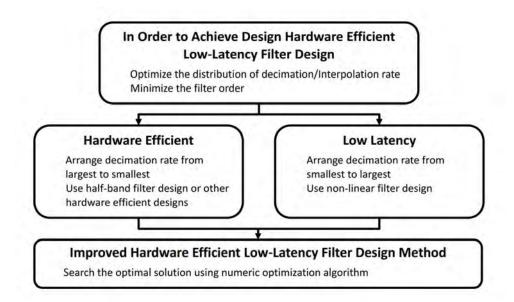

Figure 1.1: Structure of Research

As Figure 1.1 shows, in order to achieve the aim of research, the costs and latency of decimation or interpolation filters need to be minimized. According to Crochiere and Rabiner (1975), the distribution of decimation or interpolation rate affects cost and latency of the multi-stage multi-rate filter design significantly. Therefore, it is important to find out the optimal decimation or interpolation rate distribution for the design. Also, the improved of filter design will reduce the costs and latency as well.

However, cost efficient and low latency designs have contradictory design requirements. Hence, using suitable types of filters and filter design parameter optimization become the key to achieving the aim. Nevertheless, there are many design parameters need to be optimized, and each parameter's change affects the filter performance. Therefore, these parameters have to be adjusted together. Base on these characteristics, the numeric optimization algorithm is used to search the optimal solution.

Following the above research structure, the thesis are mainly constituted by six parts.

**Chapter 2 Literature Review** presents the background upon which this thesis will be developed. It begins with a discussion of the digital audio system. Different popular modulation techniques and filter requirements are introduced along with different systems. Finally, optimal decimation or interpolation rate calculation methods and optimal filter design techniques have been discussed.

Chapter 3 Methodology discusses the methodology of research work based on the 1.2 Objectives.

Chapter 4 Cost Efficient Decimation Rate Selection and Filter Design investigates into the optimal decimation or interpolation rate calculation methods and the optimal multi-stage multi-rate filter design techniques for different aspects. A highly efficient decimation or interpolation rate selection method is proposed. Lastly, based on this selection method, the look-up to 3D table optimal filter design method has been introduced.

Chapter 5 Research and Derivation for Theoretical Latency of Multi-stage Multi-rate Filter investigates into the relationship between filter's latency and filter design parameters. The derived latency estimation function for the optimal narrow band linear phase FIR filter design fills the gap. From analysis of this estimation function, the relationship between latency and filter design parameters is discovered. Also the relationship between latency and different filter costs has been discussed as well. Chapter 6 Low Latency Cost Efficient Filter Design Using Optimization Method integrates all previous findings into a realistic model based low latency cost efficient filter design framework. Meanwhile, the widening transition bandwidth and overshoot problem, the low cost filter design using half-band structure and passband ripple allocation problem have been discussed.

**Chapter 7 Conclusion and Future Work** concludes the thesis. Research problem and findings are discussed and the suggestions for future work were considered.

## **1.4 Contributions**

The main contribution of this thesis is the proposed filter design evaluation and development framework for  $\Sigma$ - $\Delta$  Modulation based high level audio ADC. In achieving this, a number of other contributions are made as follows:

• The first contribution is we proposed a new method for fast identifying the optimal decimation or interpolation factors for area cost and computational cost efficient multi-stage multi-rate filter design. This new method improved the efficiency of optimal decimation/interpolation rate selection significantly.

Author did this based on the limitations of current decimation or interpolation rate selection approaches. From 1975 to 2007, Crochiere and Rabiner and Coffey have proposed different approaches. However, they all have the complicated calculation or search process and cannot provide integer solutions. Although Huang (2003,2009) proposed exhaustive and genetic algorithm based search methods to obtain the integer solutions using set theory, this method is not ideal in efficiency.

• Second contribution is to solve the optimal latency filter design problem. To construct the relationship between filter's latency and design parameters.

The second contribution we made is because currently, there is no theoretical relationship between filter's latency and multi-stage design parameters. Therefore, my supervisor Leo Wang and I derived the latency estimation equation inspired by Crochiere and Rabiner 1975 (1975)'s assumption and filter order estimation equations. From this equation, author discovered that the key factors affect the latency performance are transition bandwidth, passband ripple and stopband attenuation. These findings guide us to design the optimal low cost and low latency filters which leads to my 3rd contribution.

• At last, based on above contributions, author proposed a numeric optimization based cost efficient low-latency filter design method to improve the performance of filter cost and latency at the same time.

The proposed method uses the annealing algorithm to optimize the key factors affect the filter performances, so that the designed filter can be further improved by about 3%-4% on the basis of previous optimal design. To the best of our knowledge, there is no theoretical framework to optimize multi-stage multi-rate filter using the properties we discovered in previous research. Although in commontial package such as MATLAB, they do use the optimization method which haven't been published. However, author proposed method shows better results than the existing software as well.

## 1.5 Publications

• Most of research in Chapter 4 was published as: Zhu, Xiangyu et al. (2016) "Practical Considerations on Optimising Multistage Decimation and Interpolation Processes". In: Digital Signal Processing (DSP), 2016 IEEE International Conference on. IEEE, pp. 370-374.

The author of the thesis wrote and did the factorisation algorithm, database creation, optimal solution set selection algorithm, as well as the implementation, analysis, and verification of the program. Yonghao Wang has discovered the regularity of optimal solution sets, and proposed the simplified search and balanced design algorithms. Other authors had and editing and supervising role. The program and data can be browsed from Zhu and Wang (2016).

• The preliminary work of Chapter 6 was published as: Ma, R. et al. (2018) "Optimum Design of Multistage Half-band FIR Filter for Audio Conversion Using a Simulated Annealing Algorithm". In: 2018 13th IEEE Conference on Industrial Electronics and Applications (ICIEA), pp. 74-78.

The author of the thesis proposed the design methods and filter design and measure algorithm. Yonghao Wang proposed the idea of using wider transition to reduce the filter cost. Rongxuan Ma proposed using simulated annealing algorithm to find out the optimal solution. Other authors had an editing and supervising role.

## Chapter 2

## Literature Review

## 2.1 Digital Audio System

According to Trick and T. (1975) and Leslie and Singh (1990), most of the real-time digital audio processing systems have the following common audio processing chain structures.

Figure 2.1: Audio Processing Chain

Lapsley et al. (1997) mentioned that there are four main blocks in the audio processing chain: analog to digital converter (ADC) module, digital signal processor (DSP) module, digital interface module and digital to analog converter (DAC) module. For audio signal processing, an anti-aliasing filter can be added into the chain if the system does require one. And with the same argument, the anti-imaging filter can be added into the chain as well.

Wang (2011) mentioned the commonly used ADC/DAC technologies in the audio processing chain normally have latency about 1ms, and this 1ms delay is significant for a low-latency audio system in some situations. Wang and Reiss (2012) have pointed out the main delay of ADC/DAC is the group delay which is generated by the structure of  $\Sigma$ - $\Delta$  Modulation (SDM) based ADC/DAC.

### 2.1.1 Traditional PCM Based Digital Audio System

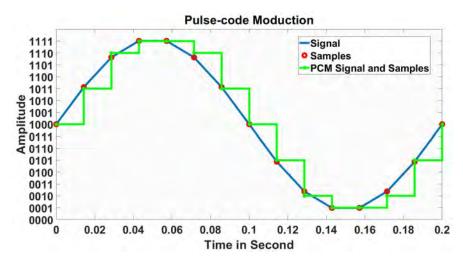

According to Mitra and Kaiser (1993) and Proakis and Manolakis (1996), in the Pulse-Code Modulation(PCM) based digital audio system, the amplitude of analogue signal is sampled regularly at uniform intervals, and each sample is quantized to the nearest value within a range of digital steps like the following example shows.

Figure 2.2: Pulse-code Modulation

As the Figure 2.2 demonstrated, the blue curve is input signal, red dots are samples and the green step signal is the PCM signal. Y axis is the amplitude of the signal, where the amplitude is represented by the binary expression of the voltage. Base on this example and theory of PCM, the lack of using PCM in high-level audio signal processing area can be found.

#### • Resolution (Bit width)

Both Lyons (2011) Leung et al. (1988) mentioned that the voltage difference between two neighbouring voltage level is very small, because the power supply can not be very large. As an example, for a 16-bit ADC/DAC with  $\pm 5$ V power supply, the range between two digital steps is only  $10V/2^{16}$  which is around 0.00015V Therefore, it is hard to separate the voltage into too many levels due to the stability and accuracy problem. According to the datasheet of Texas Instruments PCM56, normally, regulated power supplies with 1% or less ripple are recommended for use with the DAC. Hence, the highest resolution for PCM based system is around 16-bit which is far behind the  $\Sigma$ - $\Delta$  Modulation based system.

• Quantization error (Rounding error)

Also Vegte (2001) and Stein (2001) have mentioned that the samples are sampled with the fixed space in time domain, and the amplitude of samples are rounded to the nearby voltage level as the Figure 2.2 demonstrates. Even though, the difference between the sample's amplitude and nearby voltage level is tinny.

• Analogue anti-aliasing and anti-imaging filter and other support analog circuit are needed

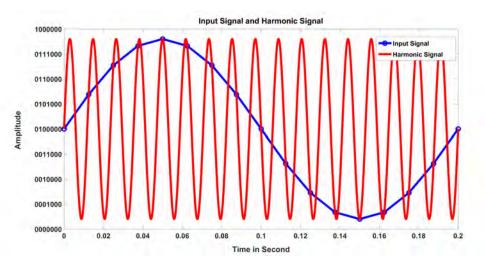

Figure 2.3: Input Signal and Harmonic Signal

According to Oppenheim, Schafer, and Buck (1999), Madisetti and Williams (1998) and Mitra (2011), as Figure 2.3 shows, the input signal is normally sampled with a certain sampling rate. Mintzer and Liu (1977) mentioned these samples can be reconstructed with different combinations of sine waves which means the non-existent high frequencies (Red harmonic signal and its harmonic signals) are added to the signal. Hence, the anti-aliasing and anti-imaging filters are needed to filter out these extra high frequencies.

Based on the Nyquist Sampling Theory, in order to abstract all information from the signal, sampling frequency of the system has to be more than two times of signal's frequency. However, the sampling frequency can not be too large due to the efficiency problem and aliasing or imaging problem. Therefore, the system's sampling frequency is usually chosen according to the limitation of Nyquist Sampling Frequency to avoid these problems.

Meanwhile, Schreier, Temes, and Norsworthy (1997) and Friedman et al. (1989) have pointed out that currently, even though lots of digital audio systems use PCM format signal as the standard, but due to the stability of voltage cannot be maintained when the resolution is higher than 16-bit, the sampling process has been replaced by  $\Sigma$ - $\Delta$  Modulation technique.

## 2.1.2 $\Sigma$ - $\Delta$ Modulation Based Digital Audio System

Candy (1986) and Stojnic and Babic (2011) stated the concept of  $\Sigma$ - $\Delta$  Modulation has been proposed for decades, but because of the limitation of Integrated Circuit (IC) in the past,  $\Sigma$ - $\Delta$  Modulation technique had been stuck in a concept for long time until the rapid development of Very Large Scale Integration (VLSI) in recent years. Now, according to Ansari and Liu (1985) Hejn, Kale, and Kurek (1993),  $\Sigma$ - $\Delta$  Modulation technique has been widely used in digital audio processing area because of its high resolution. It also reduces the design complexity of external analog anti-aliasing filter and anti-imaging filter via the internal filters. But Williams and Taylor (2006) also state that the  $\Sigma$ - $\Delta$  Modulation technique has the shortcoming of the latency of the internal filters.

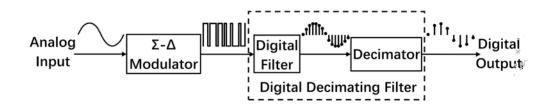

Figure 2.4: Block Diagram for  $\Sigma$ - $\Delta$  ADC

Figure 2.4 shows a typical SDM based ADC, Aziz, Sorensen, and Spiegel (1996)it can be regarded as two parts: one is the SDM modulator and the other one is digital filter (decimation filter in this case). According to Gray (1987) and Boser and Wooley (1988), for  $\Sigma$ - $\Delta$  Modulator Block, there are integrator, comparator and 1bit digital to analog converter in a negative

feedback loop. Furthermore, Candy (1985) and Chae and Han (2009) added more integrator or feedback loop of the  $\Sigma$ - $\Delta$  modulator to improve the resolution and accuracy of the system. However, comparing with the costs and latency caused by digital decimator or interpolator parts, these modifications are insignificant.

Figure 2.5: First-Order  $\Sigma$ - $\Delta$  ADC

Lipshitz and Vanderkooy (2001) stated that following the basic structure of the  $\Sigma$ - $\Delta$  modulator, like Figure 2.5 shows, the signal will be imported to the integrator after adding the input signal and the negated DAC output together; the integrator will export a ramp signal, the slope of this signal is proportional to the amplitude of the input signal of the integrator; and the output signal of integrator will be compared with the reference signal in the comparator and export 1-bit output. The binary output signal of comparator will be sent to the digital decimation filter based on the oversampling of ADC which is the rate of oversampling. Each bit of the comparator's output signal represents the direction of the output signal, after cycling for several times, the N-bit sample representation is exported from the digital decimation filter, and it represents the quantized values of the output signal. In fact, the input signal is matched with the average output of the DAC by the feedback loop, and the digital decimation filter will counterpoise the bit stream and export the N-bit samples with accepted sampling frequency.

Wherein the  $\Sigma$ - $\Delta$  Modulator block does not cause the latency, Candy and Benjamin (1981) mentioned the significant latency is caused by the internal filter which is designed as high performance, high resolution filter. Wang and Reiss (2012) have proved that the low-latency filter for  $\Sigma$ - $\Delta$  ADC can be realized mathematically, but there is no detailed literature showing if these filters can be realized in hardware concisely.

According to Kester (2000), the  $\Sigma$ - $\Delta$  ADC has the following characteristics:

- Low Cost, High Resolution (to 24-bits)

- Excellent Differential Linearity

- Low Power, but Limited Bandwidth (Voiceband, Audio)

- Key Concepts are Simple, but Math is Complex

- Oversampling

- Quantization Noise Shaping

- Digital Filtering

- Decimation

- Ideal for Sensor Signal Conditioning

- High Resolution

- Self, System, and Auto Calibration Modes

- Wide Applications in Voiceband and Audio Signal Processing

Hence, the  $\Sigma$ - $\Delta$  Modulation technique is suitable for high-level audio signal processing area. According to the view of Kester (2000), at present, there are several kinds of ADC/DAC architecture, for example, the Pulse-code Modulation based ADC/DAC, Successive Approximation Register (SAR) based ADC/DAC,  $\Sigma$ - $\Delta$  Modulation based ADC/DAC and so on. And each of these systems has different internal structures and performances. The  $\Sigma$ - $\Delta$  based ADC/DAC becomes de facto standard converters used in audio system nowadays due to its architectural advantages in supporting small and portable size of audio devices.

## 2.2 Filters

## 2.2.1 LTI Discrete-Time System

Oppenheim, Schafer, and Buck (1999) and Mitra (2011) have mentioned the linear system is the most widely used discrete-time system in digital signal processing. For high level audio signal processing area, the Linear Time-Invariant(LTI) System is the most common used system format. There are two important properties for LTI system, linearity and the time invariance.

#### • Time invariance

According to Tan and Jiang (2018), the time invariance system can be described as the follows: the output signal will be identical delay for N seconds while the input signal import to the system N seconds from now. This means there is a time-invariance system:

$$y(n) = H\{x(n)\}$$

(2.1)

The system must meet the requirement of:

$$y(n-N) = H\{x(n-N)\}$$

(2.2)

Following the above description of Time invariance, the system can simply be viewed as following figure 2.6 shows. No matter how long the signal delayed, for a certain input signal, the system will export the same output with added delay. In another word, the output signal is only related to the input signal.

Figure 2.6: Sketched Diagram of Time Invariance

This property is the basic feature of  $\Sigma$ - $\Delta$  Modulation based decimation/interpolation filter. Otherwise it will be very hard to reconstructed the filtered digital signal to desired analog signal due to the correctness of the input signal cannot be guaranteed.

#### • Linearity

Linearity describes the relationship between system's input and output is a linear map. For example, A system H which has input signal  $x_1(n)$ produces the output signal  $y_1(n)$ , and the input signal  $x_2(n)$  produces the other output signal  $y_2(n)$ . If the system meets the condition of input signal  $a_1x_1(n) + a_2x_2(n)$  producing the output signal  $a_1y_1(n) + a_2y_2(n)$ it can be called as a linear system. According to Tan and Jiang (2018), this system can be sketched as:

| x1(n)                               | System | y₁(n)                               |

|-------------------------------------|--------|-------------------------------------|

| x2(n)                               | System | y₂(n) →                             |

| $\alpha_1 x_1(n) + \alpha_2 x_2(n)$ | System | $\alpha_1 y_1(n) + \alpha_2 y_2(n)$ |

Figure 2.7: Sketched Diagram of Linear System

The system can be written as:

$$a_1y_1(n) + a_2y_2(n) = H\{a_1x_1(n) + a_2x_2(n)\}$$

(2.3)

Then, this can be extended to an arbitrary number of terms, and so for real numbers  $a_1, a_2, \ldots, a_k$

$$\sum_{k} a_k y_k(n) = H\{\sum_{k} a_k x_k(n)\}$$

(2.4)

Linearity is important for decimator or interpolator in  $\Sigma$ - $\Delta$  modulation based ADC/DAC due to the accuracy of the reconstructed signal. However, Wang and Reiss (2012) pointed out that using non-linear filter can reduce the system's latency significantly. In exchange, higher frequency signals will have larger groupdelay. This may cause discomfort in high level audio area.

As Mitra (2011) mentioned, there are two fundamental types of digital filters, the finite impulse response (FIR), and the infinite impulse response (IIR). Although it is not accurate enough, when referring to FIR filters, they usually refer to linear FIR filters. With the same argument, IIR filters normally

refer to non-linear IIR filters.

## 2.2.2 Infinite Impulse Response (IIR) Filter

As shown by the name of infinite impulse response filter, the impulse response of this type of filter extends for an infinite period of time due to the recursive structure or feedback loop. An example of IIR filter has been given in Figure 2.8. Kester (2000) has mentioned that although IIR filter can be implemented with fewer computations than FIR filters, IIR filters do not match the performance achievable with FIR filters, and there is no computational advantage when the output of an IIR filter is decimated because each output value must always be calculated. And there is one of the most important problems for using IIR filter in the audio signal processing area is IIR filter do not have linear phase.

Kester (2000) and Ifeachor and Smithson (1995) have also pointed out that the Infinite Impulse Response Filter is a highly efficient filter type. Meanwhile, IIR filter can achieve better magnitude-frequency characteristics with less hardware resources. But there are prominent characteristics for IIR filter which are non-linear phase and the performance not able to compete against FIR filter. Therefore, although IIR has the theoretical advantages comparing with FIR filter, IIR has disadvantages in applications.

Figure 2.8: Second-Order IIR Filter Simplified Notation

IIR filter's impulse response is infinite, and its transfer function can be written as: -M

$$H(z) = \frac{Y(z)}{X(z)} = \frac{\sum_{i=0}^{M} b_i z^{-1}}{1 - \sum_{j=1}^{N} a_j z^{-1}}$$

(2.5)

Where:

M is feedforward filter order  $b_i$  are feedforward filter coefficients N is feedback filter order  $a_j$  are feedback filter coefficients

According to Kester (2000), IIR filter has following characteristics:

- Uses Feedback (Recursion)

- Impulse Response has an Infinite Duration

- Potentially Unstable

- Non-Linear Phase

- More Efficient than FIR Filters

- No Computational Advantage when Decimating Output

- Usually Designed to Duplicate Analog Filter Response

- Usually Implemented as Cascaded Second-Order Sections (Biquads)

Even though, the IIR filter has advantage of cost efficient and low-latency comparing with FIR filter, Johnson (1984) point out that the accuracy of calculation and storage is required due to the feedback loop, and the stability check is needed. McClellan, Parks, and Rabiner (1973) mentioned that the IIR filter need analogue support circuit which may increase the volume of system. Also the vary latency may cause the mismatch in high level audio area. Sozanski (2013) stated that although using linear-phase IIR filters as interpolator can reduce the filter order and operations significantly, linearphase IIR filters are only suitable for applications where a linear-phase is required and long delay time is acceptable. Hence, for the  $\Sigma$ - $\Delta$  Modulation technique, IIR filter is not the best choice.

### 2.2.3 Finite Impulse Response (FIR) Filter

Mitra 2011 (2011) and Smith (1997; 2003) have mentioned that the Finite Impulse Response Filter is a kind of filter which has finite length of impulse response curve. Comparing with IIR filter, the most important advantage of FIR filter is its linear phase. But not all FIR filters have this characteristic. Only symmetrical FIR filter has this characteristic.

The most elementary form of an FIR filter is given in Figure 2.9.

Figure 2.9:  $N_{th}$  Order FIR Filter Simplified Notation

Based on the above Figure 2.9, the FIR filter's transfer function can be written as:

$$H(z) = \sum_{n=0}^{N-1} h(n) z^{-n}$$

(2.6)

According to Kester (2000), the characteristics of FIR filters can be summarized as:

- Impulse Response has a Finite Duration (N Cycles)

- Linear Phase, Constant Group Delay (N must be odd)

- No Analog Equivalent

- Unconditionally Stable

- Can be adaptive

- Computational Advantages when Decimating Output

- Easy to Understand and Design

- Windowed-Sinc Method

- Fourier Series Expansion with Windowing

- Frequency Sampling by Using Inverse FFT-Arbitrary Frequency Response

- Parks-McClellan Program with Remez Exchange Algorithm

### 2.2.4 Discussion

Kester (2000) summarized the following Table 2.1:

| IIR Filters                        | FIR Filter                      |

|------------------------------------|---------------------------------|

| More Efficient                     | Less Efficient                  |

| May Be Unstable                    | Always Stable                   |

| Non-Linear Phase Response          | Linear Phase Response           |

| No Efficiency Gained by Decimation | Decimation Increases Efficiency |

Table 2.1: Comparison Between FIR and IIR Filters

As mentioned above,  $\Sigma$ - $\Delta$  Modulation based system is widely used in audio area. Therefore high performance digital decimation or interpolation filters are needed. From section 2.2.2, it can be known that IIR filters are more efficient than FIR filters because the less memory usage and fewer multiplier are needed. However, IIR filters need extra analog support circuit and may exhibit instability problems, but this is much less likely to occur if higher order filters are designed by cascading second-order systems. On the other hand, FIR filters require more taps and multiplier for a given design. But linear phase characteristics and the steepness of transition band are the advantage of FIR filters. If the number of multiplication is not prohibitive, and the linear phase is a requirement, the FIR filter should be chosen which means for  $\Sigma$ - $\Delta$  Modulation based high-level audio ADC/DAC, FIR filters are better than IIR filters.

## 2.3 Filter Cost

With the rapid development of science and technology, high quality audio or video media are no longer a symbol of large professional equipments; rather, more and more portable devices have the capability to run or play high quality entertainment resources. Therefore, filter cost become one of the most important consideration for filter design.

## 2.3.1 Different Filter Cost

Filter cost is not only one aspect or a parameter, there are several different types of cost. For example, Computational Cost, Area Cost and so on. Each of these cost describes one or several performances of filters. This project is mainly focused on the "Computational", "Area" and "Latency" cost which are the most important evaluation factors for the filter.

#### **Computational Cost**

Oppenheim et al. (1976) pointed out that there are several different methods to evaluate the filter performance. One of the most common used method to evaluate efficiency of filter is the so called "Computational Cost" which can evaluate the computation complexity of the system. Normally, the computational cost can be expressed as A/IS (Addition per Input Sample) and M/IS (Multiplication per Input Sample). A/IS and M/IS are the addition or multiplication operation needed for each input sample during the filtering process.

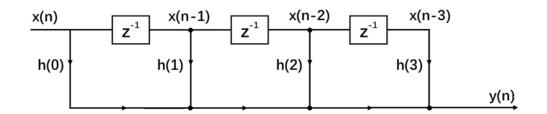

Figure 2.10:  $3_{rd}$  Order FIR Filter Simplified Notation

As above Figure 2.10 shows, for this  $3_{rd}$  order FIR filter, in order to obtain the current output signal y(n), the current input signal x(n) needs to multiply with filter coefficient h(0), and then add the accumulates of previous signals and filter coefficients in sequence which means, the current input signal x(n) needs to do one multiplication and three additions to obtain the current output signal y(n).

#### Area Cost

As Crochiere and Rabiner (1975; 1976 and 1981) mentioned, the difference between Computational Cost and Area Cost is that the "Computational Cost" represents the computation complexity and the "Area Cost" represents the hardware complexity. The "Area Cost" can be expressed as how many storage capacities are needed for the system.

As in the same example given in Figure 2.10, the filter coefficients h(0) to h(3), previous input signal x(n-1) to x(n-3) and also the accumulates of

filter coefficients and previous input signal  $x(n) \times h(0)$  to  $x(n-3) \times h(3)$  need to be stored for future operations. Memory usage and occupation can be used to present the "Area Cost".

#### Power Cost

As Brandt and Wooley (1994) mentioned, the high-level audio signal processing system pay more and more attention to portability. Therefore, most of these devices are battery driven. Hence, the battery life is an extremely important design indicator which means the system must achieve high performance with relatively low power cost.

According to Agarwal, Pavankumar, and Yokesh (2008) adders and multipliers are the most important arithmetic units in a general microprocessor and the major source of power dissipation. Yuan and Liu (2014) have pointed out that with the advancement of Very Large Scale Integrated Circuit (VLSI) design technology, high performance processing chips have become an indispensable part of communications, electronics and space technology. Therefore, modules containing a large number of decimal multiplications are also frequently applied to various chips and circuits such as digital filters and digital signal processors. For general multiplications, its power cost and area cost are mainly derived from the number of internal addition operations. Therefore, if the number of internal addition operations can be reduced while maintaining the accuracy of the multiplication operation, the power cost and area cost of the multiplier can be reduced effectively.

Therefore, the computational cost of the filter design is the key factor of power cost of filter.

### 2.3.2 Latency

The auditory perception of latency has important effects on many live audio applications. In many cases if the latency between two consequent expected events is beyond a certain threshold, it causes negative effects. Lester and Boley (2007), Farner et al. (2009), and Chafe, Caceres, and Gurevich (2010) have summarized the typical latency thresholds for different applications, for musical ensembles, the performance can be naturally synchronised when the latency is between 8ms to 25ms.

As above mentioned, Wang and Reiss (2012) have pointed out the main delay of ADC/DAC is the group delay which is caused by the filters. And the system's latency is well known as the delay between input signal and output signal. With the same example given by Figure 2.10, the filter needs four samples to start the process, therefore, the filter starts to export the output signal after importing the four input samples. This delay is so called the group delay which is the main delay of ADC/DAC for  $\Sigma$ - $\Delta$  Modulation based system due to the extreme rigorous requirements.

For a digital filter which has N sample impulse response h(n), where n is the input serial number. If we perform Discrete-time Fourier Transform (DTFT) on this filter, the following transfer function can be obtained:

$$H(\omega) = M(\omega)e^{j\phi(\omega)} \tag{2.7}$$

Where  $M(\omega)$  is the magnitude response of filter,  $\Phi(\omega)$  is phase response of filter and  $\omega$  is the angular frequency. Derivative  $H(\omega)$  to  $\omega$ , it can be obtained:

$$\frac{d[H(\omega)]}{d\omega} = M(\omega)\frac{d[e^{j\phi(\omega)}]}{d\omega} + e^{j\phi(\omega)}\frac{d[M(\omega)]}{d\omega}$$

(2.8)

After derivative expansion of the first term on the right side of the equal sign and simplifying, the equation becomes:

$$\frac{jd[H(\omega)]/d\omega}{M(\omega)e^{j\phi(\omega)}} = -\frac{d[\phi(\omega)]}{d\omega} + j\frac{d[M(\omega)]/d\omega}{M(\omega)}$$

(2.9)

Because the  $jd[H(\omega)]/d\omega$  is the DTFT of  $n \cdot h(n)$ ,  $M(\omega) \cdot e^{j\phi(\omega)}$  is  $H(\omega)$  which is DTFT of h(n) and  $-d[\Phi(\omega)]/d\omega$  is the group delay of the filter. If we use DFT instead of DTFT, the above equation 2.9 can be rewritten as:

$$GD = real[\frac{DFT[n \cdot h(n)]}{DFT[h(n)]}]$$

(2.10)

where the GD is the filter's group delay. And from this equation 2.10 it can be found that the group delay calculation method is the process of deconvolution of the phase or it can be said that the group delay is the differentiation of phase versus frequency.

According to Section 2.2.2 and 2.2.3, and also the above Equation 2.10, it can be known that the linear FIR filter has constant group delay and IIR filter has the group delay that varies with frequency due to the different phase characteristic. Although the non-linear phase filter has lower group delay comparing with linear phase FIR filters, the varies group delay makes the non-linear filter a great disadvantage for time-sensitive signals in industry control signal, live music signal and so on.

### 2.3.3 Discussion

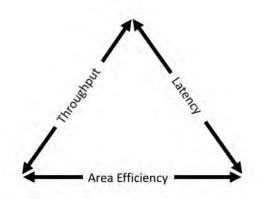

Zambreno, Nguyen, and Choudhary (2004) mentioned that cost efficient system with high throughput has higher group delay. With the same argument, the low-latency system must has larger area cost or smaller throughput. Zambreno, Nguyen, and Choudhary (2004) proposed that relationship between different filter design aspects can be sketched like following figure shows.

Figure 2.11: Relationship Between Different Filter Design Aspects

In above figure 2.11, throughput can be regarded as computational cost and area efficiency can be treat as area cost.

As mentioned above, both computational cost and area cost are highly correlated with filter order which means if the filter order can be estimated the computational cost and area cost can be estimated as well. Simultaneously, filter design parameters can be optimized to obtain the minimum filter order. Hence, the problem becomes how to estimate filter order accurately. Also, if the storage optimization and resource sharing can be involved, the area cost may further reduced.

However, as far as author knows, there is no systematic article on the latency estimation of high level audio filter. Therefore, the filter latency estimation method related with filter order is derived by author and author's supervisor Yonghao Wang. This estimation method fill the gap of correlation between area cost, computational cost and latency.

### 2.3.4 Filter Order and Estimation Functions

Base on the discussion in 2.3.3, filter order is the belt that links the area cost, computational cost, and latency of the filter. Therefore, it is very important to estimate filter order accurately. Unfortunately, filters using in  $\Sigma$ - $\Delta$  modulation based ADC/DAC have not made new breakthroughs in these decades. Hence, even though there are several filter order estimation functions can be found for filters using in  $\Sigma$ - $\Delta$  modulation based ADC/DAC, the most common used estimation function is still Crochiere and Rabiner (1975) one.

#### Crochiere and Rabiner 1975

$$N_i \cong \frac{D_{\infty}(\delta_1, \delta_2)}{\Delta F_i} - f(\delta_1, \delta_2) \Delta F + 1$$

(2.11)

Where:

$$D_{\infty}(\delta_1, \delta_2) = [5.309 \times 10^{-3} (log_{10}\delta_1)^2 + 7.114 \times 10^{-2} (log_{10}\delta_1) - 0.4761] log_{10}\delta_2 - [2.66 \times 10^{-3} (log_{10}\delta_1)^2 + 0.5941 (log_{10}\delta_1) + 0.4278]$$

(2.12)

$$\Delta F = \begin{cases} \frac{(f_{ri} - f_s) - f_p}{L_i f_{r(i-1)}} & \text{For Decimation} \\ \frac{(f_{ri} - f_s) - f_p}{M_i f_{ri}} & \text{For Interpolation} \end{cases}$$

(2.13)

$$f(\delta_1, \delta_2) = 0.51244 \log_{10}(\frac{\delta_1}{\delta_2}) + 11.01217$$

(2.14)

N is the estimated filter order.

$\Delta F$  is the transition band width normalized to the sampling frequency.  $\delta_1$  is the tolerance in the magnitude response in the passband divide  $K(\delta_p/K)$ .  $\delta_2$  is the tolerance in the magnitude response in the stopband.

For high-level audio  $\Sigma$ - $\Delta$  ADC/DAC, most of the stages will have relatively narrow-band filters. Hence,  $\Delta F$  in Equation 2.11 will be relatively small and insignificant. Therefore, the further approximation of filter order estimation equation can be written as:

$$N \cong \frac{D_{\infty}(\delta_1, \delta_2)}{\Delta F} \tag{2.15}$$

### Herrmann, Rabiner, and Chan 1973

$$N \cong -2\frac{\log_{10}(10\delta_1\delta_2)}{3\Delta F} - 1 \tag{2.16}$$

Where:

N is the estimated filter order.

$\Delta F$  is the transition band width normalized to the sampling frequency.

$\delta_1$  is the tolerance in the magnitude response in the passband.

$\delta_2$  is the tolerance in the magnitude response in the stopband.

#### Kaiser 1974

$$N \cong -20 \frac{\log_{10}(\sqrt{\delta_1 \delta_2}) - 13}{14.6\Delta F} \tag{2.17}$$

Where:

N is the estimated filter order.

$\Delta F$  is the transition band width normalized to the sampling frequency.

$\delta_1$  is the tolerance in the magnitude response in the passband.

$\delta_2$  is the tolerance in the magnitude response in the stopband.

Based on these filter order estimation functions, the filter order can be estimated accurately. According to the relationship between the filter order and different cost, the required resources can be estimated as well. Hence, it is possible to find a way to design the optimal filters with above filter order estimation functions.

## 2.4 Optimal Decimation/Interpolation Rate Calculation Methods

Lesso and Magrath (2005) and Craven (2004) pointed out that the filter order can be very large if the transition bandwidth is narrow. As the above section 2.1.2 expresses, the  $\Sigma$ - $\Delta$  ADC requires very narrow transition bandwidth due to the oversampling technique. From the tests and experiences, the filter order could be more than 1000. Therefore, it will be very hard to realize the high-level audio ADC/DAC with single stage filter design.

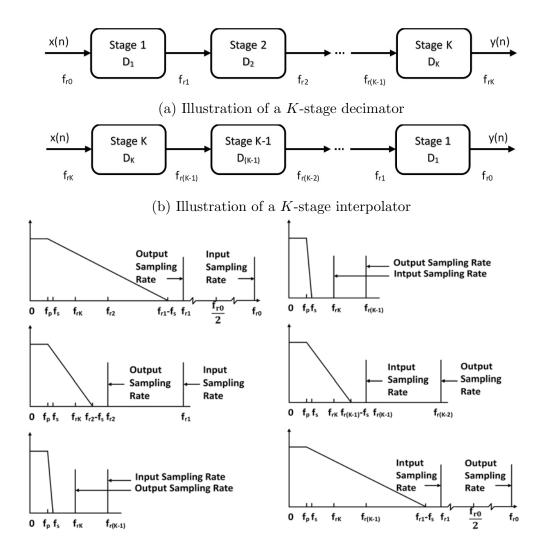

However, the multi-stage filter design technique makes the  $\Sigma$ - $\Delta$  ADC/DAC achievable with significant reduction of computational or area cost. Bellanger, Daguet, and Lepagnol (1974) and Nelson, Pfeifer, and Wood (1972) implemented decimation using several decimation stages which reduced the filter order significantly; however Crochiere and Rabiner (1975) mentioned that they restricted their results by only using factors of two at each stage. Shively (1975) considered a more general approach with integer decimation for a two stage design. Also, Rabiner and Crochiere (1975) extend and generalize the work of Shively (1975) using the more decimation stage. At that time, the filter order can be reduced to few hundreds which represents the filter cost becomes acceptable and the  $\Sigma$ - $\Delta$  modulation based ADC/DAC can be realized. Hereafter, how to design the optimal multi-rate multi-stage filter becomes the major problem. At that time, there is no affirmatory support theory to design the optimal decimation or interpolation filter mathematically. Therefore, Crochiere and Rabiner have proposed a theory to design the optimal multi-rate multi-stage filter in 1975, 1976 and 1981 (Crochiere and Rabiner 1975; 1976 and 1981). But these theories are based on the theoretical model which can be treated like the following sketched diagram.

(c) Frequency response (Decimation)(d) Frequency response (Interpolation)Figure 2.12: Sketched Block Diagram of Crochiere and Rabiner (1975)

#### 2.4.1 Optimal Computational Cost(Crochiere and Rabiner 1975)

According to Section 2.3, the filter costs are mainly caused by the filter order N. The filter order N can be estimated by using Equations 2.11, 2.16 and 2.17. Therefore, Crochiere and Rabiner (1975) convert the optimal decimation or interpolation rate selection problem into a minimum filter order finding problem.

Also, 2.11, 2.16 and 2.17 demonstrate that the key factors affect the filter order most are passband ripple, stopband attenuation and transition bandwidth. Due to the absolute values of passband ripple and stopband attenuation are fixed relatively, the transition bandwidth becomes the target to be optimized.

Hence, the sketched diagram of theoretical model for optimal multi-rate multi-stage filter design was proposed by Crochiere and Rabiner in 1975. In this model, the passband and stopband ripples are ignored as Figure 2.12 shows.

According to this model, the total computational cost  $R_T$  can be treated as the summation of each filter stage's cost  $R_i$ .

$$R_T = \sum_{i=1}^K R_i \tag{2.18}$$

And the current filter's computational cost  $R_i$  can be expressed as the product of current stage's filter order  $N_i$  times the sampling rate of the filter.

$$R_i = \frac{N_i L_i f_{r(i-1)}}{L_i M_i} = \frac{N_i f_{r(i-1)}}{M_i}$$

(2.19)

According to the above model, the transition bandwidth  $\Delta F$  can be summarized as:

$$\Delta F = \frac{(f_{ri} - f_s) - f_p}{L_i f_{r(i-1)}}$$

(2.20)

Substitute Equations 2.15 and 2.20 into 2.19, it can be obtained that:

$$R_i \cong D_{\infty}(\frac{\delta_p}{K}, \delta_s) \frac{D_i f_{ri}^2}{f_{ri} - f_s - f_p}$$

(2.21)

Hence, the total computational cost  $R_T$  can be summarized as:

$$R_T \cong D_{\infty}(\frac{\delta_p}{K}, \delta_s) f_{r0} \sum_{i=1}^K \frac{D_i}{(\prod_{j=1}^i D_j)(1 - \frac{f_s + f_p}{f_{r0}} \prod_{j=1}^i D_j)}$$

(2.22)

Assume the last stage's sampling frequency  $f_{rK}$  is equal to two times of the stopband edge  $f_s$ , it can be obtained that  $\Delta f = \frac{f_s - f_p}{f_s}$ . If we abstract the last stage from the summation part of Equation 2.22, the estimation function for the total computational cost  $R_T$  can be simplified as:

$$R_T \cong D_{\infty}(\frac{\delta_p}{K}, \delta_s) f_{r0} S \tag{2.23}$$

Where  $D_{\infty}(\frac{\delta_p}{K}, \delta_s)$  can be calculated by equation 2.12 and:

$$S = \frac{2}{(\Delta f \prod_{j=1}^{K} D_j)} + \sum_{i=1}^{K-1} \frac{D_i}{(\prod_{j=1}^{i} D_j)(1 - (\frac{2 - \Delta f}{2D}) \prod_{j=1}^{i} D_j)}$$

(2.24)

# 2.4.2 Optimal Memory Usage(Crochiere and Rabiner 1976)

With the same argument of estimation function of computational cost  $R_T$ , Crochiere and Rabiner find that the area cost can be expressed as the sum of the lengths of the filter in each stage. Therefore, Crochiere and Rabiner has proposed the estimation function for filter's area cost (memory usage) in 1976. And the approximate objective function can be written as:

$$N_T \cong G \sum_{i=1}^K N_i \tag{2.25}$$

Where  $N_T$  is the total number of necessary storage requirement,  $N_i$  is the length of the FIR filter for *i*-stage, K is the total number of stages and G is a proportionality constant.

$$N_i \approx \frac{D_{\infty}(\frac{\delta_p}{K}, \delta_s) D_i L_i}{1 - \frac{2 - \Delta f}{2D} \prod_{j=1}^i D_j}$$

(2.26)

Where D is the total upsampling or downsampling rate,  $\Delta f = (f_s - f_p)/f_s$ ,  $f_p$  is the passband edge, and  $f_s$  is stopband edge which can be assumed as

half of the final sampling frequency.

$$N_T \approx GD_{\infty}(\frac{\delta_p}{K}, \delta_s) \sum_{i=1}^{K} \frac{D_i}{1 - \frac{2 - \Delta f}{2D} \prod_{j=1}^{i} D_j}$$

(2.27)

Hence, the estimation function can be simplified to:

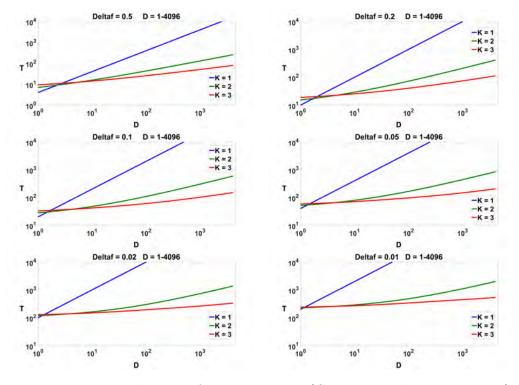

$$N_T \approx GD_{\infty}(\frac{\delta_p}{K}, \delta_s)T \tag{2.28}$$

Where  $D_{\infty}(\delta_p/K, \delta_s)$  depending only upon the stopband and passband ripple levels is only a slowly varying function of K. The key multivariable factor T can be summarized as:

$$T = \frac{2}{\Delta f} \frac{D}{\prod_{j=1}^{K-1} D_j} + \sum_{i=1}^{K-1} \frac{D_i}{1 - \frac{2 - \Delta f}{2D} \prod_{j=1}^i D_j}$$

(2.29)

Therefore, the total area cost  $N_T$  is minimized by minimizing T while the number of filter stage K is fixed.

# 2.4.3 Improved Optimal Computational Cost(Coffey 2003)

As the above part mentioned, Crochiere and Rabiner have proposed the optimal decimation or interpolation rate calculation method for optimal computational cost filter design in 1975 and 1981. According to Crochiere and Rabiner (1975; 1981), the proposed optimal decimation or interpolation rate finding problem is an optimization process. Therefore, the solution can not be found directly. Hence, Coffey (2003) has proposed another method to find the optimal decimation or interpolation rate for each stage based on Crochiere and Rabiner (1975; 1981). This approach reduces the complexity of the problem by mathematically using Partial Differential Equations (PDE).

According to Coffey (2003), for the given number of stages, the minimized computational cost  $R_T$  can be found by minimizing the multivariate function S as mentioned in Equation 2.24.

Coffey (2003) has demonstrated how to calculate the decimation or interpolation rate of each stage for optimal computational cost  $R_T$  when the filter stage is less than 5. If we assume  $f_2 = 2 - \Delta f$ , for a 2-stage filter design (K = 2), S depends only upon  $D_1$ , and the optimal solution, found by putting  $dS/dD_1 = 0$ , is given by

$$D_1 = \frac{2D}{f_2} \frac{1}{(1 + \sqrt{D\Delta f/f_2})}$$

(2.30)

$$D_2 = D/D_1 (2.31)$$

When filter stage K = 3, the factor S in Equation 2.24 can be written as:

$$S = \frac{2}{\Delta f D_1 D_2} + \frac{1}{1 - f_2 D_1 / 2D} + \frac{1}{D1(1 - f_2 D_1 D_2 / 2D)}$$

(2.32)

In order for S to be minimized, it is necessary that  $\partial S/\partial D_1 = \partial S/\partial D_2 = 0$ . Hence, two equations can be deduced.

$$D_{1}^{2}\frac{\partial S}{\partial D_{1}} = -\frac{2}{\Delta f D_{2}} + \frac{f_{2}}{2D}\frac{D_{1}^{2}}{(1 - f_{2}D_{1}/2D)^{2}} - \frac{1}{(1 - f_{2}D_{1}D_{2}/2D)} + \frac{f_{2}}{2D}\frac{D_{1}D_{2}}{(1 - f_{2}D_{1}D_{2}/2D)^{2}} = 0$$

(2.33)

$$D_2^2 \frac{\partial S}{\partial D_2} = -\frac{2}{\Delta f D_1} + \frac{f_2}{2D} \frac{D_2^2}{(1 - f_2 D_1 D_2 / 2D)^2} = 0$$

(2.34)

Therefore, according to Equation 2.34, it can be deduced that

$$D_2(D_1) = \frac{2D}{f_2} \frac{1}{(D_1 + \sqrt{D\Delta f / f_2}\sqrt{D_1})}$$

(2.35)

By combining Equations 2.33 and 2.34, the equation can be found for  $D_2$  in terms of  $D_1$ . If we combine the equation  $(D_2/D_1)\partial S/\partial D_2 = 0$  and  $\partial S/\partial D_1 = 0$ , it can be deduced

$$D_2(D_1) = \frac{\alpha D_1^2 - \alpha^2 D_1^2 + 2\alpha D_1 - 1}{\alpha^2 D_1^3}$$

(2.36)

Where  $\alpha = f_2/2D$ .

Hence, the first decimation rate or the last interpolation rate  $D_1$  can be calculated by using the combination of Equations 2.33 and 2.35 or Equations

2.34 and 2.36. Therefore  $D_2$  can be found if we substitute  $D_1$  into the equations. Finally,  $D_3$  can be solved by using the relationship between the total decimation or interpolation rate and each stage's decimation or interpolation rate which is  $D = D_1 D_2 D_3$ .

For four stages, we can still start from Equation 2.24. It can be found that:

$$D_3(D_1D_2) = \frac{2D}{f_2} \frac{1}{\sqrt{D_1D_2}(\sqrt{D_1D_2} + \sqrt{D\Delta f/f_2})}$$

(2.37)

$$D_{1}^{2} \frac{\partial S}{\partial D_{1}} = -\frac{2}{\Delta f D_{2} D_{3}} + \frac{f_{2}}{2D} \frac{D_{1}^{2}}{[1 - f_{2} D_{1}/2D]^{2}} - \frac{1}{[1 - f_{2} D_{1} D_{2}/2D]} + \frac{f_{2}}{2D} \frac{D_{1} D_{2}}{[1 - f_{2} D_{1} D_{2}/2D]^{2}} - \frac{1}{D_{2}} \frac{1}{[1 - f_{2} D_{1} D_{2} D_{3}/2D]} + \frac{f_{2}}{2D} \frac{D_{1} D_{3}}{[1 - f_{2} D_{1} D_{2} D_{3}/2D]^{2}} = 0$$

$$(2.38)$$

and

$$D_{2}^{2} \frac{\partial S}{\partial D_{2}} = -\frac{2}{\Delta f D_{1} D_{3}} + \frac{f_{2}}{2D} \frac{D_{2}^{2}}{[1 - f_{2} D_{1} D_{2}/2D]^{2}} - \frac{1}{D_{1}} \frac{1}{[1 - f_{2} D_{1} D_{2} D_{3}/2D]} + \frac{f_{2}}{2D} \frac{D_{2} D_{3}}{[1 - f_{2} D_{1} D_{2} D_{3}/2D]^{2}} = 0$$

(2.39)

Since  $D_3$  can be known from Equation 2.37, the problem becomes a two dimensional root finding problem. If we combine Equation 2.38 and 2.39, it can be found that:

$$D_2(D_1) = \frac{\alpha D_1^2 - \alpha^2 D_1^2 + 2\alpha D_1 - 1}{\alpha^2 D_1^3}$$

(2.40)

Therefore, the two dimensional root finding problem can be simplified to a one dimensional root finding problem. By combining the Equation  $(D_3/D_2)\partial S/\partial D_3 = 0$  with  $\partial S/\partial D_2 = 0$ , it can be found:

$$D_3(D_1, D_2) = \frac{\alpha D_1 D_2^2 - \alpha^2 D_1^2 D_2^2 + 2\alpha D_1 D_2 - 1}{\alpha^2 D_1^2 D_2^3}$$

(2.41)

According to Crochiere and Rabiner (1975; 1981), the filter's computational

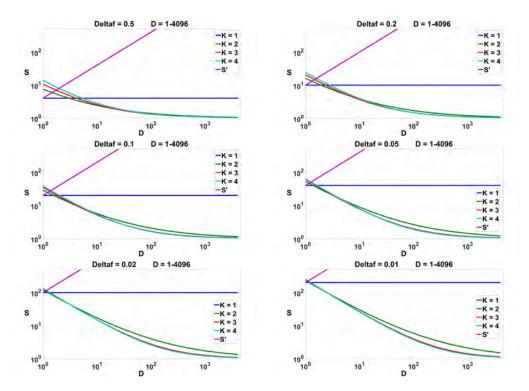

cost  $R_T$  can be decreased significantly by using multi-stage design. However, Crochiere and Rabiner (1975) also mentioned that the influence of key factor S would be reduced significantly as well while the filter had four or more stages. Hence, only 2-4 stage's solution methods are proposed by Coffey (2003).

#### 2.4.4 Improved Optimal Memory Usage(Coffey 2007)

In 2007, Coffey published another paper based on Crochiere and Rabiner (1976) and Coffey (2003) which proposed the optimal decimation or interpolation rate calculation method for area cost (storage requirement).

With the same argument of relationship between S and computational cost  $R_T$ , only 2 and 3 stages' optimal decimation or interpolation rate calculation method for area cost has been deduced by Coffey (2007).

For stage K = 2, T depends only upon  $D_1$ , therefore, the optimal solution can be found by letting  $dT/dD_1 = 0$  which is:

$$D_1(D) = \frac{2D}{f_2} \frac{1}{(1 + \sqrt{2D\Delta f}/f_2)}$$

(2.42)

$$D_2 = D/D_1 (2.43)$$

Where  $f_2 \equiv 2 - \Delta f$

When K = 3, T can be simplified to

$$T = \frac{2D}{\Delta f D_1 D_2} + \frac{D_1}{1 - \alpha D_1} + \frac{D_2}{1 - \alpha D_1 D_2}$$

(2.44)

In order to minimize the key factor T, it is necessary to make  $\partial T/\partial D_1 = \partial T/\partial D_2 = 0$ . Therefore, it can be obtained:

$$D_2(D_1) = \frac{2D}{f_2} \frac{1}{(D_1 + \sqrt{2D_1 D\Delta f}/f_2)}$$

(2.45)

By letting the result  $1 - [(2 - \Delta f)/2D]D_1D_2 = \sqrt{\Delta f D_1/2D}D_2$  from  $\partial T/\partial D_2 = 0$  into the equation  $\partial T/\partial D_1 = 0$ , latter equation can be written as:

$$\frac{\partial T}{\partial D_1} = -\frac{2D}{\Delta f D_1^2 D_2} + \frac{1}{(1 - \frac{2 - \Delta f}{2D} D_1)^2} + (\frac{2 - \Delta f}{2D}) \sqrt{\frac{2D}{\Delta f} \frac{1}{D_1} D_2} = 0 \quad (2.46)$$

#### 2.5 Summary

In this chapter, author has reviewed the background of this project. With the pursuit of high-level audio and advancement of technology, high-level audio has become one of the indispensable components of modern electronic products. However, the requirements for high resolution and low-latency make the design of high-level audio system extremely demanding. Due to the principle of PCM, the accuracy of sampling cannot be guaranteed at such a high resolution, and there is also the need for additional anti-aliasing and anti-imaging filters. This has lead to the  $\Sigma$ - $\Delta$  modulation based digital audio system gradually becoming the mainstream. The main feature of the  $\Sigma$ - $\Delta$ modulation based digital audio system is to use high sampling frequency in exchange for high resolution. At the same time, aliasing and imaging noise can be filtered out in the process of up or down sampling, thereby reducing the external support circuits. However, the  $\Sigma$ - $\Delta$  modulation based digital audio system has very stringent design requirements for filters in decimator and interpolator, which causes most of the system latency is generated by these filters. Therefore, how to reduce the latency as much as possible while meeting the design requirements has become the main difficulty in the decimation or interpolation filter design.

Based on the above literature review, author further reviewed the two major characteristics of the filter: linearity and time-invariance. Then based on these two characteristics, representative filter design types: IIR and FIR filters are briefly analysed. Among them, IIR filter has the advantage of cost efficient and low-latency, but the changing latency and stability concern make it difficult to perform well in the high-level audio area. As a linear filter, FIR filter has advantage of constant latency and high stability. However, the latency is quite high compared to the IIR filter.

Hereafter, author reviews and discusses several kinds of filter cost, and points out that the filter order is the key factor affects different costs. Therefore, the problem becomes how to reduce and estimate filter order. Since the optimal FIR filter design has not made substantial progress in recent decades, the most authoritative and accurate estimation method at this stage is the still the estimation equations proposed by Crochiere and Rabiner in 1975. While at the same time, they also proposed the method of using multi-stage filter design to reduce the filter order. Kale et al. (1995) stated this method will be able to significantly reduce a single stage filter with several thousand orders to several hundred orders with only a small increase in filter latency. This means the  $\Sigma$ - $\Delta$  modulation based digital audio system can finally be truly realized. However, in the filter design, the calculation of decimation or interpolation rate of each stage is very complicated and inefficient. Hereafter, Coffey improved the decimation or interpolation rate calculation method for optimal computational and area cost filter design in 2003 and 2007, thereby convert decimation or interpolation rate calculation from the optimization into a one-dimensional root finding. However, the result of this calculation method is still non-integer, and further rounding and selection is needed to find the optimal integer solutions. Hence, author proposed a new optimal decimation or interpolation rate selection approach which has advantage of computationally convenient and also can provide directly usable optimal integer solutions.

Meanwhile, author found that although many researchers have made a lot of research and contributions to the hardware design of low-latency filter (Peled and Liu, 1974), no researchers have proposed the latency estimation method for optimal FIR filter. Similarly, author also found that the current research on the optimization of filters is mainly focused on a certain performance of the filter rather than global optimization. However, as above mentioned, it can be known that the  $\Sigma$ - $\Delta$  modulation based digital audio system has comprehensive requirements for filters, not only for latency but also different costs and performances. Therefore, how to optimize the overall filter performance and construct a filter evaluation and design framework with only few amount of relevant literature is a great challenge.

# Chapter 3

## Methodology

As mentioned above, the current background is more and more mobile devices equipped with high quality audio, At the same time, in the professional area, more and more stringent technical indicators have been proposed. Like the latency requirement for singer and musicians' in-ear monitoring.

The  $\Sigma$ - $\Delta$  modulation based audio system is the solution to solve the highresolution requirement problem. However, the concept of the  $\Sigma$ - $\Delta$  modulation based system is using very high sampling frequency to represent the signal. Therefore, the  $\Sigma$ - $\Delta$  modulation based system need to use oversampling compared to traditional PCM based system which means the system needs decimation and interpolation process. And this process will worsen the latency performance and add extra calculations or operations.

The aim of research is to carry out a comprehensive evaluation as well as to propose a framework for the digital filter design with both low latency and low cost for  $\Sigma$ - $\Delta$  Modulation based ADC/DAC. Following above mentioned requirements and limitations, the research question is How to design a cost efficient low-latency multi-stage multi-rate filter? If this question is asked in detail, it will lead us to the following 3 questions:

- 1. Can the parameter selection be improved?

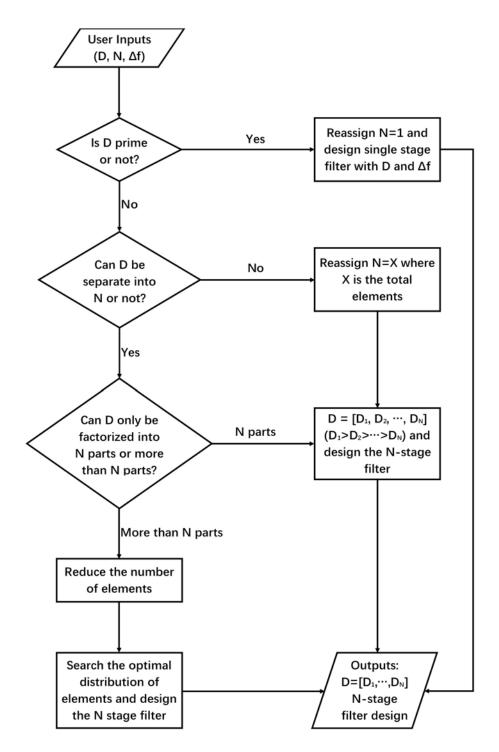

- 2. How to trade off contradictory design requirements?

- 3. Is there any existing design or trade off method can meet both low latency and hardware efficient design requirements?